- #ALLWINNER A64 CORTEX A53 1080P#

- #ALLWINNER A64 CORTEX A53 PDF#

- #ALLWINNER A64 CORTEX A53 MANUAL#

- #ALLWINNER A64 CORTEX A53 ANDROID#

#ALLWINNER A64 CORTEX A53 ANDROID#

a heavily modified AArch64 kernel, based on Linus' v3.10 release, plus Linaro LSK patches plus Android patches. a (not-mainlined) ARM Trusted Firmware port, based on the outdated v1.0 release. a hacked 32-bit U-Boot port, based on the 2014.07 release. PRCM: MMIO address mentioned in the A64 manual, IP description in the A83T manual.Īllwinner's BSP release contains source code of:. RSB: MMIO address and IRQ mentioned in the A64 manual, IP description in the A83T manual. Some devices in the SoC are not described there, but have descriptions in other SoC's manuals: #ALLWINNER A64 CORTEX A53 MANUAL#

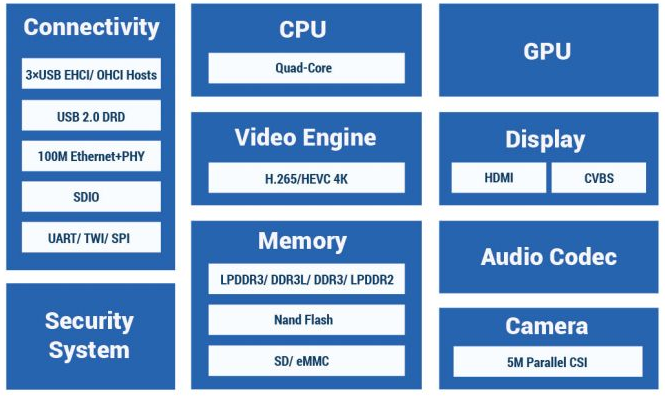

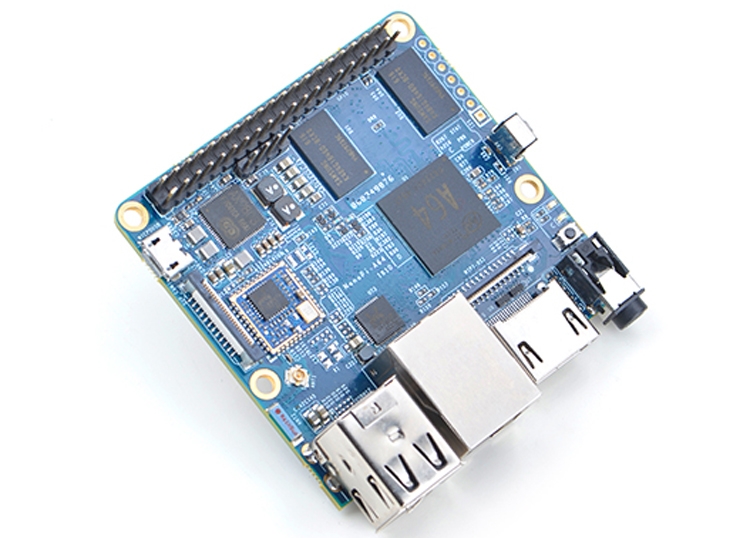

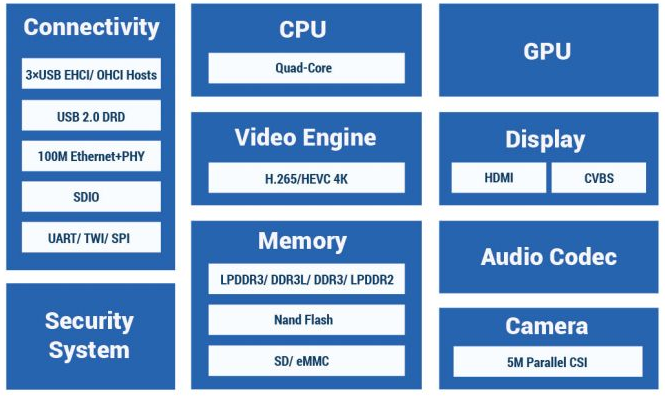

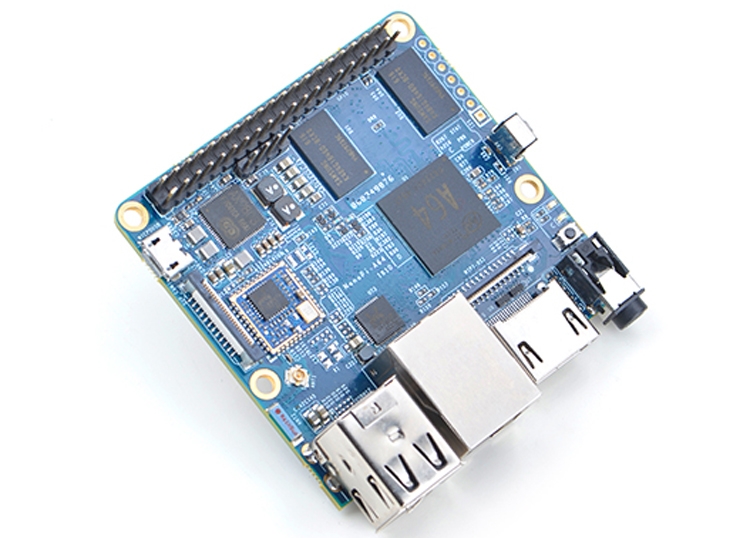

The above mentioned manual details most peripherals. A64 Hardware Development Materials (Chinese).File:Allwinner A64 User Manual V1.1.pdf.Both are quad core Cortex A53 processors with a Mali-400MP2 GPU, H.265 4K video playback with basically the same interfaces and peripherals, but H64 also supports H.264 at 4K resolutions, while A64 is limited to H.264 and H64 adds a TS interface. X-Powers AXP803, as seen used with A64 in Olimex Olinuxino A64 designĪllwinner H64 is targetted for OTT boxes and A64 for the tablets.

#ALLWINNER A64 CORTEX A53 1080P#

Maximum video capture resolution up to 1080p PMIC. Support CCIR656 protocol for NTSC and PAL. LVDS single link up to 1366x768 RGB with DE/SYNC up to 1920x1200 MIPI DSI 4-lanes up to 1920x1200 HDMI1.4 with HDCP1.2 up to 4k Camera. DDR2/DDR3/DDR3L/LPDDR2/LPDDR3 controller (up to 3GB of 667MHz(DDR-1333)). Featuring 1 vertex shader (GP) and 2 fragment shaders (PP). Affected by one critical erratum (only in AArch64 state): 843419.  Cryptography Extension (SHA and AES instructions). SIMD NEON (including double-precision floating point), VFP4. 32KiB (Instruction) / 32KiB (Data) L1-Cache per core.

Cryptography Extension (SHA and AES instructions). SIMD NEON (including double-precision floating point), VFP4. 32KiB (Instruction) / 32KiB (Data) L1-Cache per core. #ALLWINNER A64 CORTEX A53 PDF#

ARM Cortex-A53 Quad-Core (r0p4, revidr=0x80) (scroll down for the PDF link).

A prominent example is (the debug) UART0, which is on PortA on the H3, but on PortB on the A64.

The pinmux configuration is still somewhat similar, but differs to an extent which makes them incompatible. The A64 has its BROM mapped at address 0, SRAM A1 is mapped right behind it at 0x10000 (64KB). The H3 has SRAM A1 mapped at address 0, the BROM is at 0xffff0000. The MMC clocks have changed on the way, now the MMC controller itself provides support for the output and sample phase. The MMC controller has been updated to support faster transfer modes. The H3 supports 5 UARTs, the A64 has 6 of them. Despite being a 64-bit chip, this makes the SoC entirely 32-bit on the physical side. The H3 DRAM controller supports up to 2GB of RAM, the A64 supports up to 3 GB. Both SoCs have an additional USB-OTG controller, which is assumed to be used as normal host controller as well. The H3 has three USB host controllers, whereas the A64 has only one. Differences between the H3 and the A64 seem to be: They share most of the memory map, clocks, interrupts and also uses the same IP blocks. The A64 is basically an Allwinner H3 with the Cortex-A7 cores replaced with Cortex-A53 cores ( ARM64 architecture).

0 kommentar(er)

0 kommentar(er)